Thursday, August 28, 2008

Jitter and Eye Measurements: Ideal Recovery Clock

signal jitter specifications are specified relative to an Ideal Recovery

Clock defined below. The Data jitter is not specified numerically, but

instead, an High-Definition Multimedia Interface (HDMI) device or cable

shall adhere to the appropriate eye diagram(s) when the Transition

Minimized Differential Signaling (TMDS) data signals are measured using an

Ideal Recovery Clock as a trigger source.

The Transition Minimized Differential Signaling (TMDS) Clock signal may

contain low-frequency jitter components, which can be tracked by a Sink's

clock recovery circuitry, and high-frequency components, which are not

typically tracked. The purpose of the Ideal Recovery Clock is to give an

accurate representation of link performance when used as a trigger for eye

diagram and clock jitter specifications. The eye mask specifies the

relationship of clock jitter to data jitter only indirectly.

For the purposes of jitter and eye diagram specification, the Ideal

Recovery Clock is defined relative to the Transition Minimized Differential

Signaling (TMDS) clock signal. The Ideal Recovery Clock shall be equivalent

to the signal that would be derived by a perfect PLL (Ideal Clock Recovery

Unit) with a jitter transfer function shown in 'Jitter Transfer Function'

Equation, when the Transition Minimized Differential Signaling (TMDS) clock

signal were input into that PLL. This jitter transfer function has the

behavior of a low pass filter with 20dB/decade roll-off and with a –3dB

point of 4MHz.

(See attached file: Jitter Transfer Function of ideal CRU.jpg)

For the purposes of compliance testing, a Clock Recovery Unit is used to

generate a Recovered Clock, which is meant to approximate the Ideal

Recovery Clock. This Recovered Clock is used for measurement of the jitter

and eye diagram.

Wednesday, August 20, 2008

Transition Minimized Differential Signaling Overview (TMDS Overview)

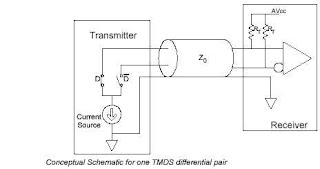

Signaling) differential pair is shown in 'Conceptual Schematic for one TMDS

differential pair' Figure. (See attached file: Conceptual schematic for one

TMDS differential pair.jpg)TMDS technology (transition minimized

differential signaling technology) uses current drive to develop the low

voltage differential signal at the Sink side of the DC-coupled transmission

line. The link reference voltage AVcc sets the high voltage level of the

differential signal, while the low voltage level is determined by the

current source of the HDMI Source and the termination resistance at the

Sink. The termination resistance (RT) and the characteristic impedance of

the cable (Z0) must be matched.

A single-ended differential signal, representing either the positive or

negative terminal of a differential pair, is illustrated in 'Single-ended

differential signal' Figure. The nominal high-level voltage of the signal

is AVcc and the nominal low-level voltage of the signal is (AVcc - Vswing).

Since the swing is differential on the pair, the net signal on the pair has

a swing twice that of the single-ended signal, or 2 Vswing. The

differential signal, as shown in 'Differential signal' Figure, (See

attached file: Differential signal.jpg) swings between positive Vswing and

negative Vswing.

The signal test points for a TMDS link (Transition Minimized Differential

Signaling Link) are shown in 'TMDS Link Test Points' Figure. (See attached

file: TMDS Link Test Points.jpg) TP1 is used for testing of HDMI Sources

and Transmitter components. TP2 is used for testing of HDMI Sinks and

Receiver components. TP1 and TP2 together are also used for testing of

cables.

Tuesday, August 19, 2008

High Definition Multimedia Interface - HDMI Physical Layer Electrical Specification

rate of the link while others are based on absolute values. For scalable

timing parameters based on the TMDS clock rate (Transition Minimized

Differential Signaling Clock Rate), the time period of the clock is denoted

as 'TMDS character time', or, 'Transition Minimized Differential Signaling

Character Rate', or Tcharacter. One tenth of the character time is called

the bit time, or Tbit. The bit time is also referred to as one Unit

Interval in the jitter and eye diagram specifications.

Schematic diagrams contained in this chapter are for illustration only and

do not represent the only feasible implementation.

Transition Minimized Differential Signaling Overview (TMDS Overview)

The conceptual schematic of one TMDS (Transition Minimized Differential

Signaling) differential pair is shown in 'Conceptual Schematic for one TMDS

(Transition Minimized Differential Signaling) differential pair' Figure.

(See attached file: Conceptual schematic for one TMDS differential

pair.jpg) TMDS technology (transition minimized differential signaling

technology) uses current drive to develop the low voltage differential

signal at the Sink side of the DC-coupled transmission line. The link

reference voltage AVcc sets the high voltage level of the differential

signal, while the low voltage level is determined by the current source of

the HDMI Source and the termination resistance at the Sink. The termination

resistance (RT) and the characteristic impedance of the cable (Z0) must be

matched.

A single-ended differential signal, representing either the positive or

negative terminal of a differential pair, is illustrated in 'Single-ended

differential signal' Figure. (See attached file: Single-ended differential

signal.jpg) The nominal high-level voltage of the signal is AVcc and the

nominal low-level voltage of the signal is (AVcc - Vswing). Since the swing

is differential on the pair, the net signal on the pair has a swing twice

that of the single-ended signal, or 2 Vswing. The differential signal, as

shown in 'Differential signal' Figure, (See attached file: Differential

signal.jpg) swings between positive Vswing and negative Vswing.

The signal test points for a TMDS link (Transition Minimized Differential

Signaling Link) are shown in 'TMDS Link Test Points' Figure. (See attached

file: TMDS Link Test Points.jpg) TP1 is used for testing of HDMI Sources

and Transmitter components. TP2 is used for testing of HDMI Sinks and

Receiver components. TP1 and TP2 together are also used for testing of

cables.

High Definition Multimedia Interface - HDMI Physical Layer

Connectors

A device's external HDMI - high-definition multimedia interface -

connection shall be presented via one of the three specified HDMI

(high-definition multimedia interface) connectors, Type A, Type B or Type

C. This connector can be attached directly to the device or can be attached

via a cable adapter that is shipped with the device.

All three connectors carry all required HDMI signals (high-definition

multimedia interface signals), including a TMDS link (Transition Minimized

Differential Signaling links). The Type B connector is slightly larger and

carries a second TMDS link (Transition Minimized Differential Signaling

links), which is necessary to support very high-resolution displays using

dual link. The Type C connector carries the same signals as the Type A but

is more compact and intended for mobile applications.

Passive cable adapters between connector types are specified.

High Definition Multimedia Interface - HDMI Physical Layer Connector

Support Requirements

All features and functions are equally available to all three connectors.

High Definition Multimedia Interface - HDMI Physical Layer Dual-Link

To support DVI signals greater than 165Mpixels/sec, the dual-link

capability of the Type B connector shall be used. To support DVI signals

less than or equal to 165Mpixels/sec, single-link operation shall be used.

To support very high-speed HDMI signals (high-definition multimedia

interface signals), the dual-link capability of the Type B connector is

available. The single-link to dual-link crossover frequency for HDMI

(high-definition multimedia interface) will be defined in a future

specification and will be greater than 340Mpixels/sec. Dual-link cannot be

used for formats below that crossover frequency.

Saturday, August 16, 2008

High-Definition Multimedia Interface (HDMI) Overview

As shown in "HDMI Block Diagram" Figure, the HDMI - high-definition multimedia interface - cable and connectors carry four differential pairs that make up the TMDS data and clock channels. These channels are used to carry video, audio and auxiliary data. In addition, HDMI high-definition multimedia interface carries a VESA DDC channel. The DDC is used for configuration and status exchange between a single Source and a single Sink. The optional CEC protocol provides high-level control functions between all of the various audiovisual products in a user’s environment.

Audio, video and auxiliary data is transmitted across the three TMDS data channels. A TMDS clock, typically running at the video pixel rate, is transmitted on the TMDS clock channel and is used by the receiver as a frequency reference for data recovery on the three TMDS data channels. At the source, TMDS encoding converts the 8 bits per TMDS data channel into the 10 bit DC-balanced, transition minimized sequence which is then transmitted serially across the pair at a rate of 10 bits per TMDS clock period.

Video data can have a pixel size of 24, 30, 36 or 48 bits. Video at the default 24-bit color depth is carried at a TMDS clock rate equal to the pixel clock rate. Higher color depths are carried using a correspondingly higher TMDS clock rate. Video formats with TMDS rates below 25MHz (e.g. 13.5MHz for 480i/NTSC) can be transmitted using a pixel-repetition scheme. The video pixels can be encoded in either RGB, YCBCR 4:4:4 or YCBCR 4:2:2 formats.

In order to transmit audio and auxiliary data across the TMDS channels, HDMI - high definition multimedia interface - uses a packet structure. In order to attain the higher reliability required of audio and control data, this data is protected with a BCH error correction code and is encoded using a special error reduction coding to produce the 10-bit word that is transmitted.

Basic audio functionality consists of a single IEC 60958 L-PCM audio stream at sample rates of 32kHz, 44.1kHz or 48kHz. This can accommodate any normal stereo stream. Optionally, HDMI - high definition multimedia interface - can carry such audio at sample rates up to 192KHz and with 3 to 8 audio channels. HDMI - high definition multimedia interface - can also carry an IEC 61937 compressed (e.g. surround-sound) audio stream at bit rates up to 24.576Mbps. HDMI - high definition multimedia interface - can also carry from 2 to 8 channels of One Bit Audio and a compressed form of One Bit Audio called DST.

The DDC is used by the Source to read the Sink’s Enhanced Extended Display Identification Data (E-EDID) in order to discover the Sink’s configuration and/or capabilities.